Основные характеристики

- Четыре высокопроизводительные системы на кристалле — четыре цифровых сигнальных процессора (DSP) TMS320C6457 Texas Instruments (TI) с частотой до 1,2 ГГц

- До 9,6 млрд. операций в секунду над операндами с фиксированной запятой

- По

64-х разрядному банку памяти DDR2 256 Мбайт на каждый DSP - Модуль

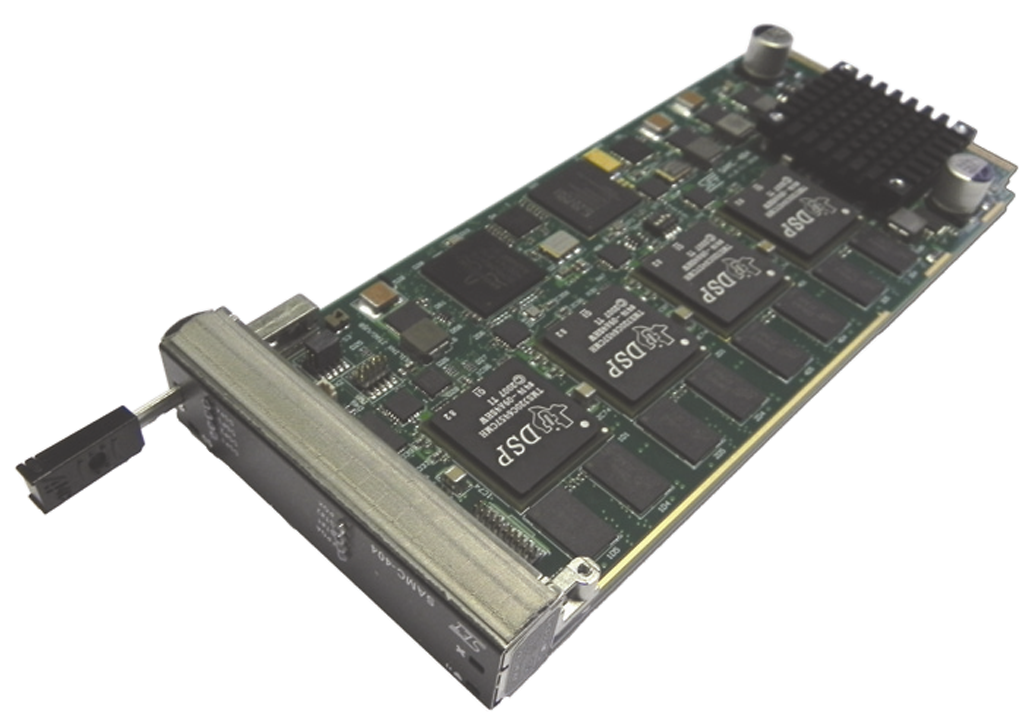

форм-фактора AdvancedMC SingleMid-Size/Full-Size для MicroTCA и AdvancedTCA систем - Поддержка системных интерфейсов: Gigabit Ethernet, SRIO 1.3 x4

Описание

Особенности

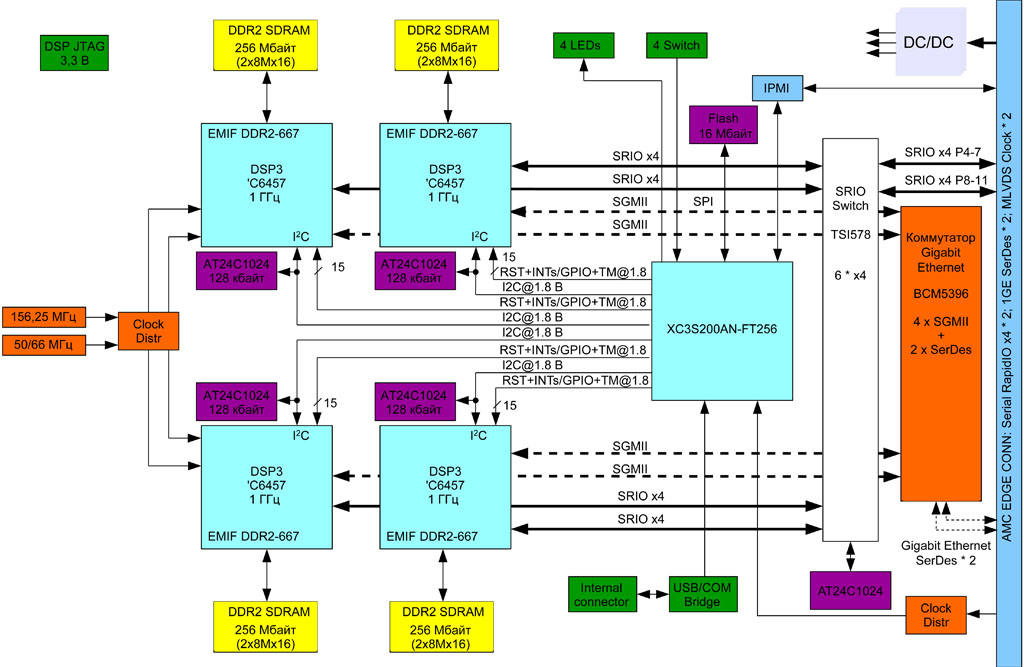

Модуль оснащен четырьмя DSP процессорами TMS320C6457CMH для работы с сигналами в реальном масштабе времени. Четыре DSP процессора, которые объединены высокоскоростными интерфейсами SRIO и Gigabit Ethernet. Каждый DSP имеет независимую память типа DDR2 объёмом 256 Мбайт.

Предусмотрена начальная загрузка DSP из индивидуальных микросхем EEPROM типа AT24C1024, ёмкостью 1024 кбит (128 кбайт) подключенных по интерфейсу I2C. Шина I2C каждого из DSP подключена к FPGA — содержимое памяти доступно для чтения/записи из DSP и из FPGA. Возможна загрузка DSP процессора по Ethernet.

Реализован диагностический интерфейс USB с FPGA через мост

Области применения

Модуль цифровой обработки сигналов