Основные характеристики

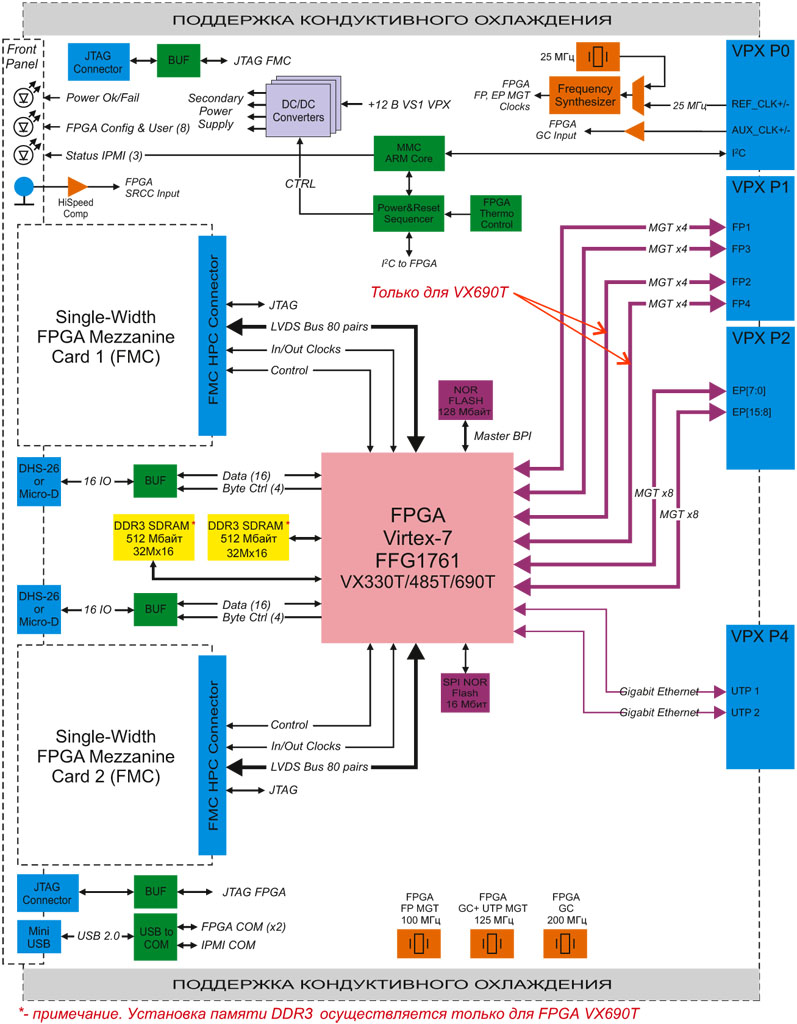

- Высокопроизводительная FPGA Xilinx

Virtex-7 в корпусе FFG1761 с поддержкой кристаллов из ряда XC7VX330/485/690T - Память FPGA — два

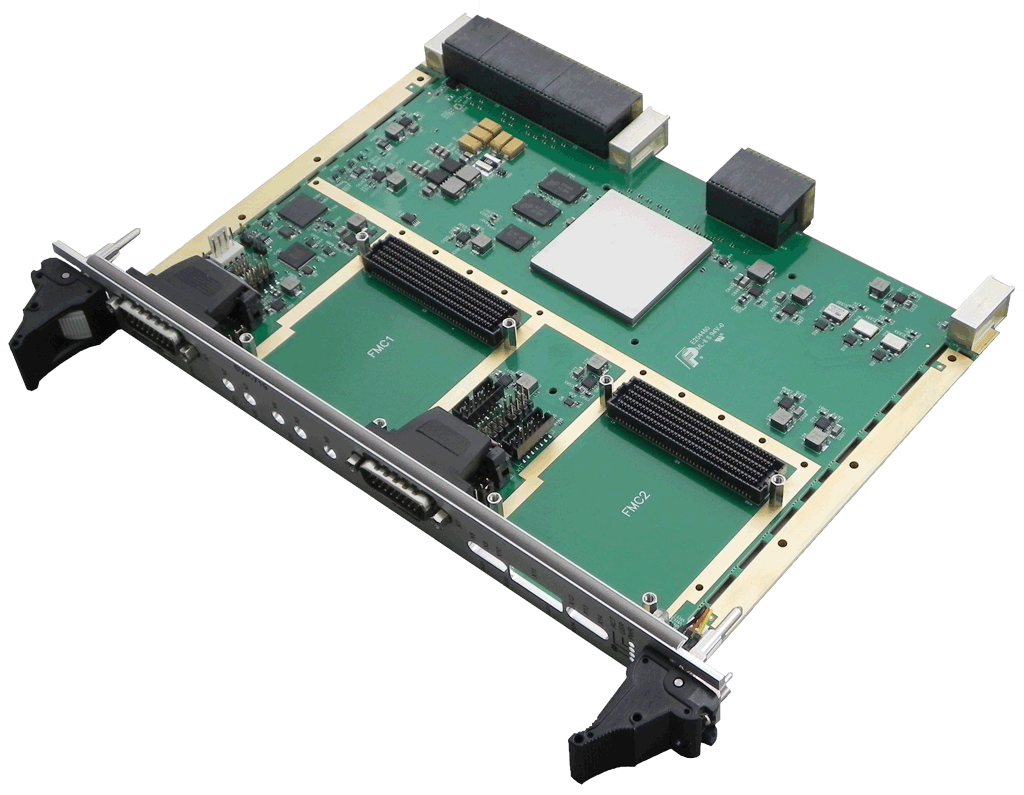

16-и разрядных банка DDR3 SDRAM до 512 Мбайт каждый в исполнении с FPGA XC7VX690T - Модуль форм-фактора VPX 3U, соответствующий стандартам:

ANSI/VITA

46.0-2013 (воздушное охлаждение), ANSI/VITA46.3-2012 , ANSI/VITA46.4-2012 , ANSI/VITA46.6-2013 , ANSI/VITA57.1-2010 и ANSI/VITA65-2010 (R2012) - Установка двух субмодулей FMC в соответствии со стандартом

ANSI/VITA

57.1-2010 с реализаций интерфейса LVDS HPC, поддержка MGT на FMC не предусмотрена - Поддержка широкого спектра системных интерфейсов:

PCIe / SRIO / XAUI, Gigabit Ethernet (отдельно приобретаемые

IP-ядра ) - Поддержка интерфейсов межплатного кольцевого соединения в крейте: Aurora x8

10 Гбит/с к соседним модулям через линии EP разъёма VPX P2 - Два

16-ти разрядных буферизованных цифровых порта - Исполнение с воздушным охлаждением

Описание

Особенности

Модуль

Производительность

Модуль

Модулем поддерживается широкий ряд интерфейсных стандартов VPX: PCIe вплоть до 3.0

(за искл. VX485T), SRIO, XAUI и Gigabit Ethernet, которые, в зависимости от типа

коммутаторов и объединительных плат, могут сочетаться между собой в различных комбинациях

(реализация интерфейсов осуществляется с помощью

Модуль поддерживает межплатное кольцевое соединение в составе крейта через линии EP[15:0]

разъёма VPX P2 с реализацией протокола Xilinx Aurora с суммарной скоростью обмена

с соседними модулями до 160

Пропускная способность интерфейса FPGA модуля с каждым субмодулем FMC достигает

80

Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через объединительную плату, географическая адресация и т. д., значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных и военных применений.

Модуль