Основные характеристики

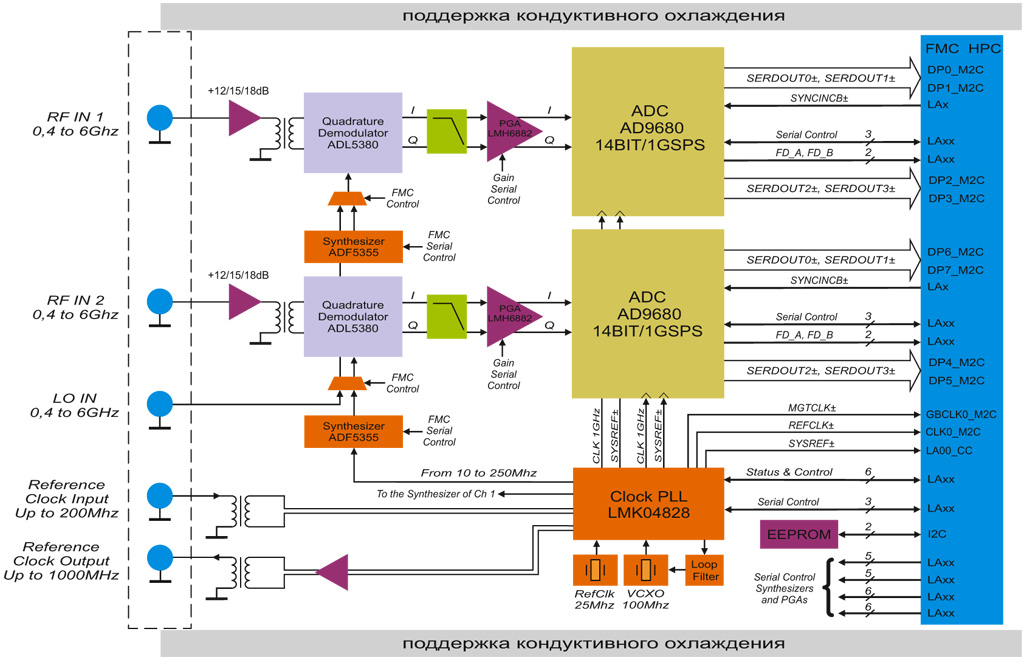

- Два независимых канала приёма аналоговых радиосигналов c квадратурным демодулятором, усилителем и АЦП 14 бит 1000 МГц

- Рабочая полоса частот: 400...6000 МГц, полоса сигнала до 400 МГц

- Интерфейс с несущим модулем JESD204B

- Поддержка встроенных в АЦП функций цифровой децимации и АРУ

- Программное управление настройками усилителя, синтезатора демодулятора, АЦП и схемой тактирования

- Вход сигнала внешнего гетеродина на передней панели для организации многоканального когерентного радиоприёма

Форм-фактор FMC одиночной ширины с воздушным или кондуктивным охлаждением

Описание

Субмодуль

Разложение входных радиосигналов на квадратуры выполнено с использованием широкополосных демодуляторов

ADL5380 Analog Devices. По выходу демодулятора наряду с ФНЧ

Подобная организация трактов наряду с применением сдвоенных микросхем АЦП AD9680 AD позволяет

достичь отличных показателей в части идентичности квадратурных каналов по амплитуде и фазовому

разбалансу, что вкупе с широкой полосой входного сигнала (до 400 МГц по −3 дБ) делает

применение субмодуля весьма перспективным для построения широкополосных систем связи, анализа

радиосигналов, а также ФАР. Последовательный интерфейс микросхем АЦП,

соответствующий стандарту JESD204B, предполагает установку на несущем модуле FPGA с поддержкой

гигабитных последовательных интерфейсов, что значительно упрощает организацию обмена АЦП

и FPGA на высоких частотах оцифровки данных. Параметры интерфейса JESD204B АЦП, равно

как и ряд других параметров АЦП, гибко настраиваются посредством интерфейсов SPI

с несущим модулем. Микросхемы АЦП предоставляют пользователю возможность первичной цифровой

обработки данных ЦАП непосредственно внутри микросхемы, для чего содержат по четыре

децимирующих, гибко настраиваемых, цифровых фильтра комплексных сигналов в составе умножителя

на

Гибкая схема узла тактирования АЦП на базе двухступенчатой ФАПЧ позволяет работать как с источником внешнего тактирования частотой от 10 МГц до 200 МГц, так и от встроенного высокостабильного опорного генератора частотой 25 МГц. Для систем с требованиями по когерентности каналов по высокой частоте (ФАР) предусмотрен вход частоты внешнего гетеродина через коаксиальный разъём SSMC на передней панели субмодуля.